Generadores y Detectores de Paridad

jueves, 4 de junio de 2020

Generadores y Detectores de Paridad

Los circuitos electrónicos digitales se basan en la transmisión y el procesamiento de información, lo que hace necesario verificar que la información recibida es igual a la emitida; no suelen producirse errores, por lo que cuando ocurren en la mayoría de los casos el error en la transmisión se produce en un único bit.

El método más sencillo y eficaz de comprobación de la transmisión de datos consiste en añadir a la información transmitida un bit más, con la misión de que el número de 1 transmitidos en total sea par (paridad par), o impar (paridad impar).

Detectores/generadores de paridad

En los generadores de paridad la paridad puede ser par o impar. El bit de paridad se utiliza para detectar posibles errores en la transmisión del dato transmitido, mediante un comprobador de paridad que recepciona la información con el fin de validarla.

Aplicacion

Los generadores de paridad se usan en Telecomunicaciones para detectar, y en algunos casos corregir errores en la transmisión de datos.

Aplicacion

Los generadores de paridad se usan en Telecomunicaciones para detectar, y en algunos casos corregir errores en la transmisión de datos.

-Paridad par

El bit de paridad será un 0 si el número total de 1 a transmitir es par.La suma de los bits que son unos, contando datos y bit de paridad dará siempre como resultado un número par de unos.

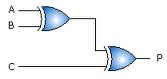

En la siguiente figura se muestra como se puede realizar un generador de paridad con puertas lógicas or-exclusiva (OR-X).

-Paridad impar

El bit de paridad será un 1 si el número total de 1 es impar, el número de unos (datos + paridad) siempre debe ser impar.

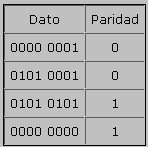

Los generadores de paridad par son aquellos circuitos que generan un 0 cuando el número de 1 en la entrada es par y un 1 cuando es impar, en el caso de dos bit, sería como se muestra en la tabla de verdad:

P = paridad par, es decir un número de 1 par.

I = paridad impar, es decir un número de 1 impar.

Las funciones canónicas serán:

Cuya posible implementación se muestra en la figura:

Como venimos comentando a lo largo de todo el tema estos circuitos no se suelen cablear, sino que se presentan como circuitos integrados.

Ejemplos

Tenemos el dato original 0111001. Vemos que la trama a transmitir tiene un número par de unos (4). Al añadir el bit de paridad obtendremos el siguiente carácter, que es el que se transmitirá a destino:

- Si usamos paridad par, ya hay un número par de unos, por tanto se añade un 0, y transmitiremos 00111001.

- Si usamos paridad impar, como hay un número par de unos, hemos de añadir otro 1 para conseguir un número impar, y transmitiremos 10111001.

Otro ejemplo de generadores de paridad sería el CI 74180.

Suscribirse a:

Entradas (Atom)